# RN8209C/RN8209D User Manual

Data: 2016-01-26 Rev: 3.5

# Update Log

| Version | Time       | Contents                             |

|---------|------------|--------------------------------------|

| V3.5    | 2016-01-26 | Translated from Chinese version V1.5 |

# **Table of Contents**

| 1 Introduction                                 |    |

|------------------------------------------------|----|

| 1.1 Features                                   | 4  |

| 1.2 Functions                                  |    |

| 1.3 Block Diagram of Functions                 | 5  |

| 1.4 Pin Definitions                            |    |

| 1.5 Typical Application                        |    |

| 2 System Functions                             | 10 |

| 2.1 Power Supply Monitoring                    | 10 |

| 2.2 System Reset                               | 11 |

| 2.3 Analog-digital conversion                  |    |

| 2.4 Active Power                               |    |

| 2.5 Reactive Power                             | 13 |

| 2.6 RMS                                        | 13 |

| 2.7 Energy Calculation                         | 14 |

| 2.8 Channel Switch                             | 15 |

| 2.9 Frequency Measurement.                     | 15 |

| 2.10 Zero-crossing Detection                   | 15 |

| 2.11 Interrupt                                 | 15 |

| 2.12 Register                                  |    |

| 2.12.1 List of Registers                       | 16 |

| 2.12.2 Calibration parameter registers         |    |

| 2.12.3 Measurement parameter registers         | 26 |

| 2.12.4 Interrupt Register                      | 30 |

| 2.12.5 System Status Register                  | 31 |

| 2.12.6 Special commands                        |    |

| 3 Calibration Methods                          |    |

| 3.1 Overview                                   |    |

| 3.2 Calibration Flow and Parameter Calculation |    |

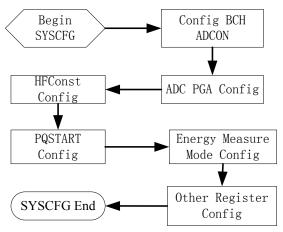

| 3.2.1 Calibration Flow                         | 33 |

| 3.2.2 Parameter Settings                       |    |

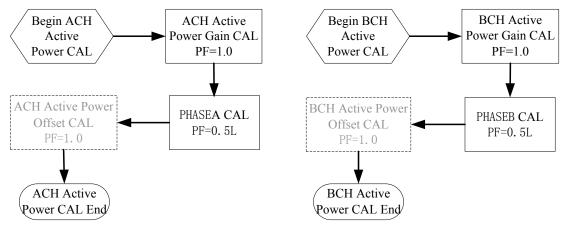

| 3.2.3 Active Calibration                       |    |

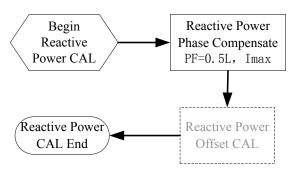

| 3.2.4 Reactive Calibration                     |    |

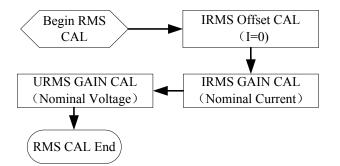

| 3.2.5 RMS Calibration                          |    |

| 3.3 Examples                                   |    |

| 4 Communication Interfaces                     | 37 |

| 4.1 SPI Interface                              |    |

| 4.1.1 Descriptions of SPI Interface Signals    |    |

| 4.1.2 SPI Frame Format                         |    |

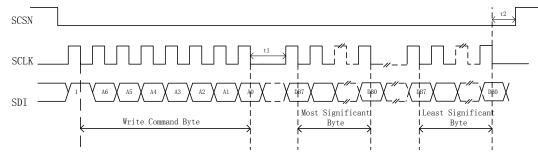

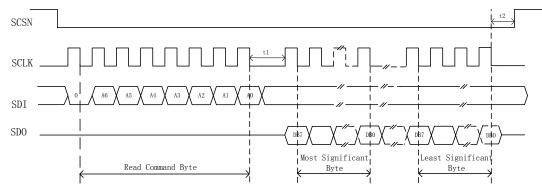

| 4.1.3 SPI Write Operation                      |    |

| 4.1.4 SPI Read Operation                       | 39 |

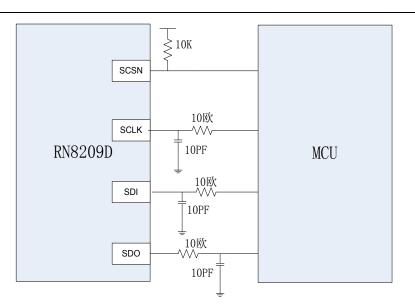

| 4.1.5 SPI Interface Reliability Design         |    |

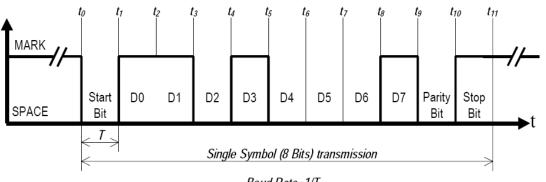

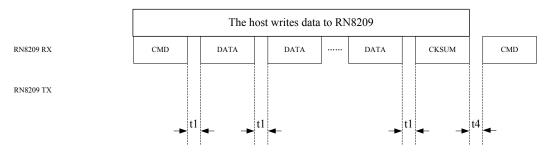

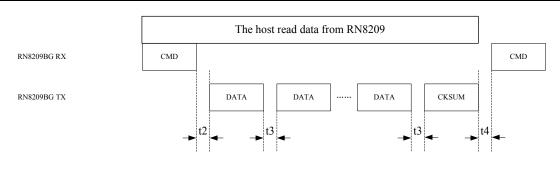

| 4.2 UART Interface                             | 40 |

| 5 Electrical Specification                     | 43 |

| 6. Package                                     | 46 |

|                                                |    |

# **1** Introduction

# 1.1 Features

- √ Measurement

- **■** Three channels of  $\Sigma$ - $\triangle$  ADC are provided.

- The active energy accuracy is less than 0.1% (< 0.1%) over a dynamic range of 8000:1 with the IEC62053-22: 2003 Standard supported.

- The reactive energy accuracy is less than 0.1% (< 0.1%) over a dynamic range of 8000:1 with the IEC62053-23: 2003 Standard supported.

- Two-channel current and one-channel voltage RMS is provided, with the RMS accuracy <0.1% over the 1000:1 dynamic range.</p>

- One pulse frequency generator which can be used for user-defined power electrical energy accumulation points.

- Provide instantaneous sample values of the three-way ADC.

- No-load threshold is adjustable.

- Reverse active power indication is provided.

- Provide voltage channel frequency measurement.

- Provide voltage channel zero-crossing detection.

- Reference baseline monitoring function

- $\sqrt{}$  Software meter calibration

- The meter constant (HFConst) is adjustable.

- Gain and phase calibration is provided.

- Offset calibration is provided for active, reactive and RMS.

- Acceleration is provided for small-signal meter calibration.

- Automatic checksum is provided for configuration parameters.

- $\sqrt{}$  SPI/UART interfaces are provided

- $\sqrt{}$  Power supply monitoring is provided

$\sqrt{\Box}$  Energy registers have timed freeze function

# $\sqrt{}$ UART's RX input pin along with pin reset function

$\sqrt{\Box}$  RN8209 + 5V / 3.3V power supply, the power consumption is typically 15mW @ 5V, 8mW @ 3.3V

$\sqrt{100}$  Built-in 1.25V ± 1% reference voltage, with typical temperature coefficient of 5ppm / °C,

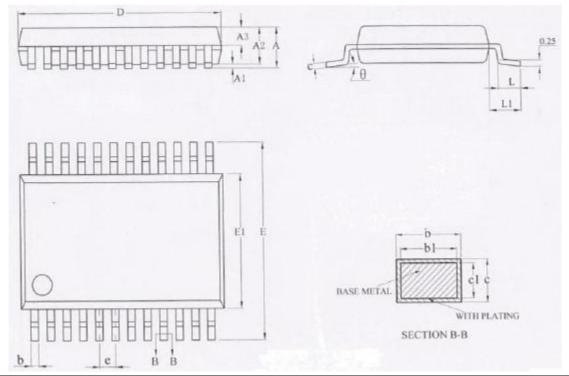

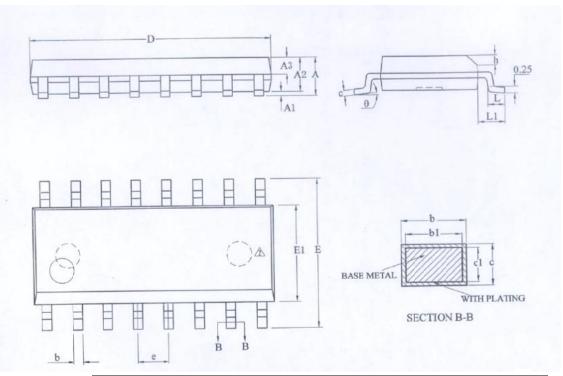

$\sqrt{}$  SSOP24 lead-free package is adopted for RN8209D, SOP16 lead-free package is adopted for RN8209C.

# 1.2 Functions

RN8209 can measure active power, reactive power, active energy and reactive energy, and can provide two-channel independent active power and RMS, voltage RMS, line frequency, zero-crossing interrupt, etc. to achieve flexible anti-tampering solutions.

RN8209 supports all-digital gain, phase and offset calibration, with the active and reactive energy pulses

respectively output from the pins of PF and QF.

RN8209D provides two serial interfaces SPI and UART, to facilitate communication with the external MCU.RN8209C provides only one serial interfaces UART, and the baud rate is fixed at 4800bps

The internal power supply monitoring circuit of RN8209 can ensure reliable operation of the chip when power on and off.

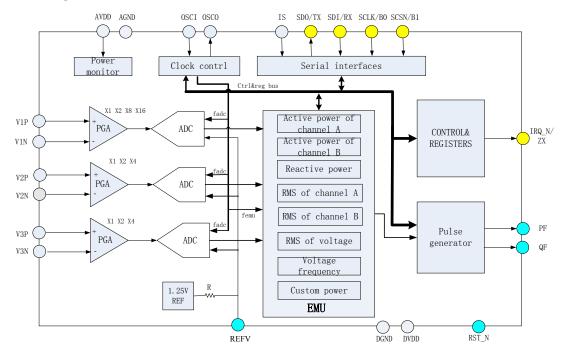

## **1.3 Block Diagram of Functions**

Figure 1-1 Block Diagram of system

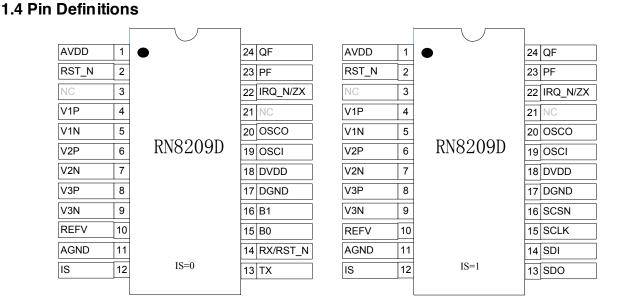

Figure 1-2 RN8209D-SSOP24 Pin Assignment

| Pins | Signs            | Features     | Function Descriptions                                                                                                                                                                                                                                                                                                                                                                                       |

|------|------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | AVDD             | Power supply | The pin of analog power supply is used to provide power supply to the analog portion of the chip. This pin should use an external 10µF capacitor and a 0.1µF capacitor paralleled for decoupling. The normal application range should be: 3V-5.5V. When the typical power supply voltage (e.g. 5V or 3.3V) is selected, the fluctuation of the power supply should be guaranteed in the range of $\pm$ 10%. |

| 2    | RST_N            | Input        | Reset pin, active at a low level. When at a low level, the chip is in a reset state. The pin should be connected to an external pull-up resistor.                                                                                                                                                                                                                                                           |

| 3    | NC               | NC           | Not connected                                                                                                                                                                                                                                                                                                                                                                                               |

| 4,5  | V1P,<br>V1N      | Input        | Positive and negative analog input pins of current Channel A - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                        |

| 6,7  | V2P,<br>V2N      | Input        | Positive and negative analog input pins of current Channel B - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                        |

| 8,9  | V3P,V3N          | Input        | Positive and negative analog input pins of the voltage channel - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                      |

| 10   | REFV             | Input/Output | 1.25V reference voltage input and output pins – The external reference source can be directly connected to this pin. Whether internal or external reference source is adopted, this pin should use a $1\mu$ F capacitor and a $0.1\mu$ F capacitor paralleled for decoupling.                                                                                                                               |

| 11   | AGND             | Power supply | Analog ground                                                                                                                                                                                                                                                                                                                                                                                               |

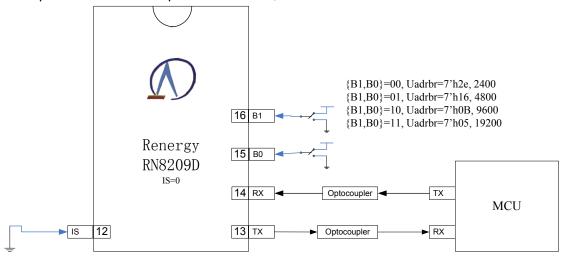

| 12   | IS               | Input        | Serial communication type selection pin – it is used to determine the communication interface type of the chip.<br>If IS = 0, choose UART as the communication interface;<br>if IS = 1, choose SPI as the communication interface.<br>Internal floating, external pull-up or pull-down is demanded.                                                                                                         |

| 13   | SDO/TX           | Output       | SDO and TX multiple xed pins,<br>When IS = 1, this pin will act as SPI serial data output SDO. After<br>reset, this pin features a high impedance output.<br>When IS = 0, it will act as TX the data output pin of the serial<br>interfaces UART                                                                                                                                                            |

| 14   | SDI/RX<br>/RST_N | Input        | When IS = 1, this pin will be an SPI serial data input SDI, which is a $3.3V/5V$ compatible pin.<br>When IS = 0, RX the data input pin of the serial interfaces UART, it is also the reset pin, which is a $3.3V/5V$ compatible pin. The interior reset circuit and UART communication circuit of RN8209D is fully independent, the reset function of this pin is the same as independent reset pin.        |

# Table 1-1 RN8209D-SSOP24 Pin Functions

| 15 | SCLK/B0      | Input                                                                                                                                                                                                                                                                                                                                                                                                     | When IS = 1, this pin will act as an SPI serial clock input pin, which<br>is a 3.3V/5V compatible pin.<br>When IS = 0, it will act as B0 which combined with B1 is used to<br>determine the baudrate of UART.<br>{B1,B0}=00 2400 baudrate {B1,B0}=01 4800 baudrate<br>{B1,B0}=10 9600 baudrate {B1,B0}=11 19200 baudrate                                                                                                                    |  |  |  |

|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 16 | SCSN/B1      | Input                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>When IS = 1, this pin will be for an SPI chip-select signal pin (active at a low level), as well as a 3.3V/5V compatible pin.</li> <li>Internal floating, an external pull-up is demanded.</li> <li>When IS = 0, this pin will act as B1, see the description of B0.</li> </ul>                                                                                                                                                    |  |  |  |

| 17 | DGND         | Power supply                                                                                                                                                                                                                                                                                                                                                                                              | Digital ground                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 18 | DVDD         | Power supply Digital power supply pin - Used to provide power supply to the digital part. This pin should have an external 10µF capacitor and a 0.1µF capacitor paralleled for decoupling. The normal application range should be: $3V-5.5V$ . When the typical power supply voltage (e.g. 5V or 3.3V) is selected, the fluctuation of the power supply should be guaranteed in the range of $\pm 10\%$ . |                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| 19 | OSCI         | Input                                                                                                                                                                                                                                                                                                                                                                                                     | Input terminal of external crystal or external clock input – The crystal frequency is typically 3.579545MHz. External capacitor is typically 15Pf ~ 22pF, the interior has about 4M ohm resistor jumper, jumper no need to add external resistors. Require external crystal ESR of less than 50 ohms.                                                                                                                                       |  |  |  |

| 20 | OSCO         | Output                                                                                                                                                                                                                                                                                                                                                                                                    | The output of an external crystal.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 21 | NC           | NC                                                                                                                                                                                                                                                                                                                                                                                                        | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 22 | IRQ_N<br>/ZX | Output                                                                                                                                                                                                                                                                                                                                                                                                    | Interrupt / indicator output when a zero-crossing is detected - After reset, it will serve as an interrupt pin.<br>when Zxcfg = 0 (EMUCON-bit7) as an interrupt request IRQ_N;<br>When Zxcfg = 1 (EMUCON-bit7), it will serve as ZX: it will output a                                                                                                                                                                                       |  |  |  |

| 23 | PF           | Output                                                                                                                                                                                                                                                                                                                                                                                                    | <ul> <li>signal when a zero-crossing in voltage channel is detected.</li> <li>Pulse output of active energy, low-level output by default. It's frequency will indicate the value of transient active power, able to achieve a 5mA output and current sinking.</li> </ul>                                                                                                                                                                    |  |  |  |

| 24 | QF           | Output                                                                                                                                                                                                                                                                                                                                                                                                    | Pulse output of reactive energy or pulse output of user-defined<br>energy, low-level output by default. It frequency will indicate the<br>value of transient reactive power or of transient user-defined power.<br>User-defined power can be select as active power of the second<br>channel, vector sum of active power of the two channels the<br>user-defined power register. It is able to achieve a 5mA output and<br>current sinking. |  |  |  |

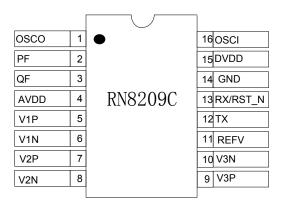

Figure 1-3 RN8209C-SOP16L Pin Assignment

| Pins | Signs    | Features       | Function Descriptions                                                                                                                                                                                                                                                                                                                                                                                       |

|------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | OSCO     | Output         | The output of an external crystal.                                                                                                                                                                                                                                                                                                                                                                          |

| 2    | PF       | Output         | Pulse output of active energy, low-level output by default. It's frequency will indicate the value of transient active power, able to achieve a 5mA output and current sinking.                                                                                                                                                                                                                             |

| 3    | QF       | Output         | Pulse output of reactive energy, low-level output by default. It frequency will indicate the value of transient reactive power, able to achieve a 5mA output and current sinking.                                                                                                                                                                                                                           |

| 4    | AVDD     | Power supply   | The pin of analog power supply is used to provide power supply to the analog portion of the chip. This pin should use an external 10µF capacitor and a 0.1µF capacitor paralleled for decoupling. The normal application range should be: 3V-5.5V. When the typical power supply voltage (e.g. 5V or 3.3V) is selected, the fluctuation of the power supply should be guaranteed in the range of $\pm$ 10%. |

| 5,6  | V1P, V1N | Input          | Positive and negative analog input pins of current Channel A - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                        |

| 7,8  | V2P, V2N | Input          | Positive and negative analog input pins of current Channel B - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                        |

| 9,10 | V3P,V3N  | Input          | Positive and negative analog input pins of the voltage channel - A fully differential input mode is adopted, the maximum input in normal operation Vpp is $\pm$ 1000mV, and the maximum withstand voltage is $\pm$ 6V.                                                                                                                                                                                      |

| 11   | REF V    | Input/Output   | 1.25V reference voltage input and output pins – The external reference source can be directly connected to this pin. Whether internal or external reference source is adopted, this pin should use a $1\mu$ F capacitor and a $0.1\mu$ F capacitor paralleled for decoupling.                                                                                                                               |

| 12   | TX       | Output         | TX the data output pin of the serial interfaces UART.                                                                                                                                                                                                                                                                                                                                                       |

| 40   | DW/DGT X | 1              | RX the data input pin of the serial interfaces UART, also the reset<br>pin of the chip, when the input level of this pin is maintained at low<br>for more than 20msm, the RN8209C will reset.                                                                                                                                                                                                               |

| 13   | RX/RST_N | RX/RST_N Input | The interior reset circuit and UART communication circuit of RN8209C is fully independent, the reset function of this pin is the same as independent reset pin.                                                                                                                                                                                                                                             |

| 14   | GND      | Ground         | Ground of chip, be attention that the pin should not be directly<br>connected to the decoupling capacitor of DVDD and other<br>ground points with lots of digital noise, but to keep away from<br>those.                                                                                                                                                                                                    |

| 15   | DVDD     | Input          | Digital power supply pin - Used to provide power supply to the digital part. This pin should have an external $10\mu$ F capacitor and a 0.1 $\mu$ F capacitor paralleled for decoupling. The normal application range should be: 3V-5.5V. When the typical power supply voltage (e.g. 5V or 3.3V) is selected, the fluctuation of the power supply                                                          |

|    |      |       | should be guaranteed in the range of $\pm 10\%$ .                                                                                  |                                                                    |

|----|------|-------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|    |      |       | Input terminal of external crystal or external clock input – The crystal frequency is typically 3.579545MHz. External capacitor is |                                                                    |

| 16 | OSCI | Input | typically 15Pf ~ 22pF, the interior has about 4M ohm resistor                                                                      |                                                                    |

|    |      |       |                                                                                                                                    | jumper, jumper no need to add external resistors. Require external |

|    |      |       | crystal ESR of less than 50 ohms.                                                                                                  |                                                                    |

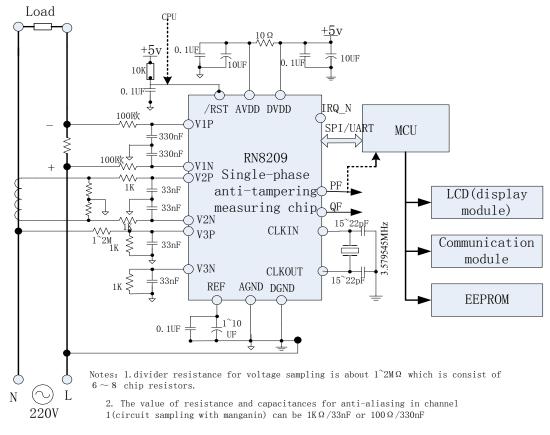

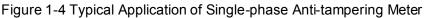

# **1.5 Typical Application**

# **2 System Functions**

# 2.1 Power Supply Monitoring

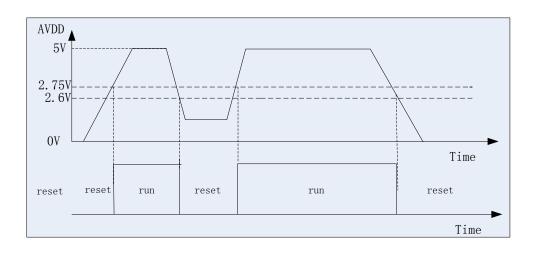

The RN8209 includes an internal power supply monitoring circuit, able to continuously monitor the analog supply (AVDD). When the power supply is lower than  $2.6V \pm 0.1V$ , the chip will be reset, and when the supply is higher than  $2.75V \pm 0.1V$ , the chip will work normally.

Figure 2-1 Power Detection Features

$\Box$  Normal range of applications: 3V-5.5V, the selected typical supply voltage (eg, 5V or 3.3V), should ensure the power fluctuation within ± 10% range.

## 2.2 System Reset

RN8209 supports three global reset methods:

- Power ON/OFF

- External pin reset or RX Pin Reset

- Reset command

When any global reset occurs, the register will be restored to its reset initial value, and the external pins will recover to the initial states.

Chip reset will be completed after 15us it received the reset command.

The external reset pin of RN8209D should go from high to low for more than 50us, and then turn to high for 300us to complete reset actions.

The RX pin of RN8209C/D is also a reset pin, when the input signal to this pin is low for more than 20ms, it will be taken as reset command. This feature saves the number of optocouplers in isolated applications. RN8209C/D internal reset circuit and UART communication circuit is completely independent, this pin reset function is exactly the same as individual pin reset.

Suggested RX pin reset operation is: first to keep RX pin low for 25ms, then high for 20ms, and finally start a normal UART communications.

#### **Relevant registers:**

In the system status register, RST is a reset sign: when the external RST\_N pin or the power-on reset has ended, this bit will be set as 1, cleared after read and can be used as a meter calibration data request after reset.

It is recommended CPU to conduct a reset operation by pin reset or reset command before initializing the measurement chip.

## 2.3 Analog-digital conversion

RN8209 includes three channels of ADC, respectively used for phase current sampling, neutral current sampling and voltage sampling. The bit of ADC2ON in the system control register is used to turn on/off the current Channel B.

ADC uses a fully differential input. The current and voltage channels have the maximum signal input amplitude at 1000mv of the peak.

By configuring bit5 ~ bit0 in the system control register (SYSCON 0x00H), the gain magnification of the three channels of ADC can be configured separately with 1, 2, 8, and 16 for current channel A, 1, 2, and 4 for current channel B and voltage channel. The current Channel A has its gain magnification as 16 times by default.

## 2.4 Active Power

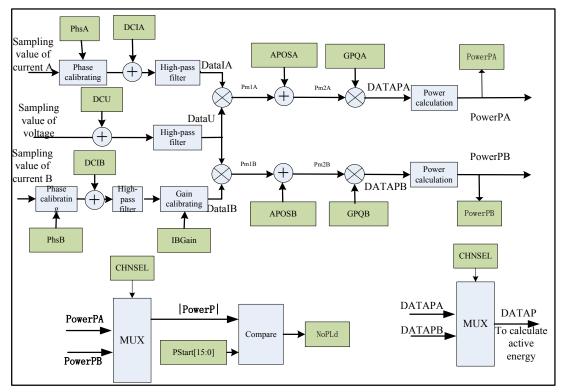

Figure 2-2 Active Power Diagram

RN8209C provides two channels of active power calculation and correction, respectively, the active power calculation and calibration of Current A and voltage, and the active power calculation and calibration of Current B and voltage.

Registers also contain two sets (A / B) of phase calibration, active offset calibration, active gain calibration and average power registers. In addition, in order to ensure the consistency of the two channels, it also provides the gain calibration register IBGain of the current channel B which can affect active power and current effective value of channel B.

The special commands can be used to determine which channels of the average active power (PowerP) currently used to determine the no-load and start status, as well as the instantaneous active power channel (DATAP) currently used to calculate the active energy come from, with the details referring to the section related to special commands.

Users can select and configure the channels by special commands, and the configuration results can be queried by the CHNSEL register bit.

The digital high-pass filter in the diagram is mainly used to remove the DC component in current and voltage sampling data.

The DIA, DIB and DCU in figure are used for ADC channel's DC bias correction. When RN8209C/D is used for DC measurement applications, users should commit DC bias correction and turn off the high-pass filter.

# 2.5 Reactive Power

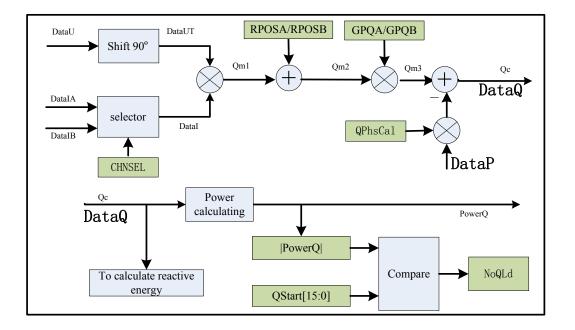

Figure 2-3 Reactive Power Diagram

RN8209 contains a circuit for reactive power measurement. Therein, the DataUT for measurement results from 90 degrees' phase shift of DataU; DataI comes from DataIA or DataIB, which can be configured by special commands, and the configuration results can be queried by the CHNSEL register bit.

# 2.6 RMS

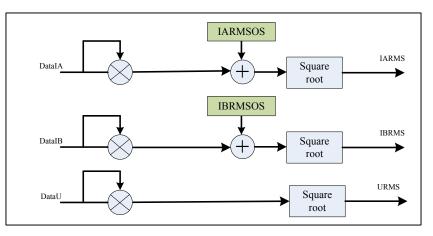

Figure 2-4 RMS Calculation Diagram

RN8209 provides the true RMS parameter output of three channels, including URMS, IARMS and IBRMS. The register length is 24bit, refresh - at 3.495Hz or 13.982Hz. In addition, it also includes two RMS Offset registers: IARMSOS and IBRMSOS.

Note: The gain calibration of channel B (IBGain) will affect the IBRMS output, but phase calibration, power gain calibration and power offset calibration will have no effect on the RMS calculation results.

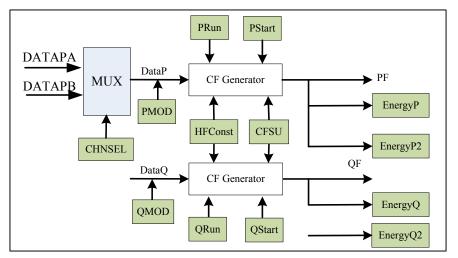

# 2.7 Energy Calculation

Figure 2-4 Energy Calculation

# Energy pulse output:

The pulse output, namely, the meter calibration pulse output, can be directly connected to a standard meter for error comparison.

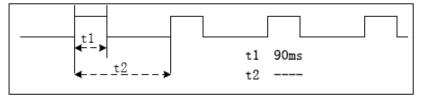

The PF / QF output meets the following timing relationship:

Figure 2-5 The width of output pulse

Note: When the pulse output period is less than 180ms, the pulse will be output in form of equal duty.

#### PFcnt, HFConst, pulse output and energy registers have the relationship as follows:

When 2\*|PFcnt| (0x20H) = HFConst (0x03H), PF has a pulse output. Simultaneously, the energy registers EnergyP (0x29H) and EnergyP2 (0x2AH) will increase 1respectively.

When 2\*|QFcnt| (0x21H) = HFConst (0x03H), QF has a pulse output. Simultaneously, the energy registers EnergyQ (0x2BH) and EnergyQ2 (0x2CH) will increase 1 respectively.

#### Relationship among pulse output, energy register, PRun / QRun and PStart / QStart:

Active / reactive energy registers and PF / QF output are also controlled by PRun / QRun and PStart / QStart.

- When PRun = 0 or |P| is less than PStart, PF does not output any pulse; PFcnt and active registers will not be increased.

- When QRun = 0 or |Q| is less than QStart, QF does not output any pulse; QFcnt and reactive energy registers will not be increased.

#### Custom pulse output:

Shenzhen RENERGY Micro-Technology Co., Ltd.

# The default source of DataD is DataD DATAQ (reactive power), you can set it's source to DATAPA (the active power of channel 2), DATAPA + DATAPB (the vecor sum of the active power of the two channels), D2FP (defined by user) by register D2FM.

#### Pulse output speedup:

To speed up the calibration of small-signal, it provides the function of pulse output speedup. While correcting small signals, you can configure **CFSUEN** and **CFSU [1:0]** bits of the EMUCON (0x01H) register, so that the PF / QF output frequency could be increased, by 16 times at most.

#### Indicating of negative power:

When the active or reactive power is negative, the EMUStatus register will have its REVP bit or REVQ bit changed to 1, with REVP bit and PF pulse, as well as REVQ bit and QF pulse synchronously refreshed.

## 2.8 Channel Switch

RN8209 specially provides one channel of ADC used for measurement of neutral current RMS and active power, and provides the function to switch the phase current and neutral current channels for users to choose which current they like to measure the active energy.

The current channels can be switched by special commands, with the details referring to the section for special command registers. The configuration results can be queried by the register bit CHNSEL.

#### 2.9 Frequency Measurement

RN8209 can directly output line frequency parameter (UFreq 0x25H 2 bytes lenth), measurement of fundamental frequency and measurement bandwidth of  $250Hz_{\circ}$  The minimum measuring frequency is 6.8Hz.

#### 2.10 Zero-crossing Detection

Configure ZXCFG (EMUCON.7) of RN8209D to enable/disable zero-crossing output of pin IRQ\_N / ZX .

Configure ZXD1 (EMUCON.9) and ZXD0 (EMUCON.8) register bits of RN8209D to select four kinds of zero-crossing output.

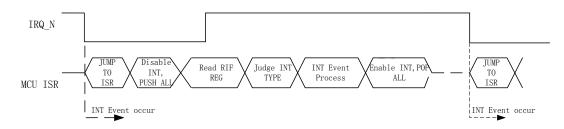

#### 2.11 Interrupt

The interrupt of RN8209D includes an interrupt enable register IE, 2 interrupt status register IF and RIF, a multiplex interrupt request pin IRQ\_N / ZX. Wherein, RIF is associated with IF, for example when reading RIF can clear IF, or vice versa.

#### 1. The interrupt request signal IRQ\_N

IRQ\_ N / ZX pin is a multiplexing pin of IRQ and zero-crossing detection output ZX, which can be configured by the ZXCFG bit of EMUCON register (0x01H).

When the corresponding interrupt bits of the interrupt enable register is enabled and the corresponding interrupt events occur, the IRQ\_N pin will output low level, and it will turn to high level until the falling edge of SCLK of the last bit (LSB) of the command which was send by CPU through SPI interface to read RIF or IF.

#### 2.Interrupt Processing

#### Hardware:

- The IRQ\_N of RN8209D is usually connected to the MCU external interrupt pin /INT, and when IRQ\_N is changing from high to low, the MCU will generate the /INT interrupt.

- The MCU serves as a SPI or UART Host, while RN8209D as an SPI or UART slave.

Shenzhen RENERGY Micro-Technology Co., Ltd. Page 15 of 47

#### Interrupt handler:

Step 1: MCU interrupt initialization

1. The MCU reads RN8209D RIF to clear IF and RIF interrupt flags;

2 Configure RN8209D IE register to enable the necessary interrupt permit bit to generate IRQ\_N;

3. The MCU enables the / INT external interrupt to wait for RN8209D interrupt event occurring. The IRQ N output triggers the / INT interrupt, and jump into the /INT interrupt entry address.

Step 2: MCU interrupt service procedure

1 Close MCU global interrupt and /INT interrupt;

2. The MCU reads RIF register via the SPI to clear the IF and RIF registers and to make sure the IRQ\_N back to a high level.

3. The MCU determines RN8209D interrupt source by the RIF interrupt flag, and then execute the corresponding interrupt handler.

4. After the interrupt handler has been executed, the MCU will enable the global interrupt and /INT interrupt again, and back to normal program after it have restored the status of CPU registers.

After interrupt return, if any /INT interrupt flag is detected, the program will enter the external interrupt ISR, and repeat 2. If no /INT interrupt flag is detected, it indicates that there is no interrupt event occurring in interrupt processing, and the program will continue

#### Figure 2-6 RN8209D Interrupt Processing

# 2.12 Register

#### 2.12.1 List of Registers

| Address | Name    | R/W        | Length      | Reset<br>Value | Descriptions                                                 |

|---------|---------|------------|-------------|----------------|--------------------------------------------------------------|

|         | Ca      | alibratior | n Parameter | and Measure    | ment Control Registers                                       |

| 00H     | SYSCON  | R/W        | 2           | 0003h          | System control register, write-protect                       |

| 01H     | EMUCON  | R/W        | 2           | 0003h          | Energy measure control register, write-protect               |

| 02H     | HFConst | R/W        | 2           | 1000h          | High frequency impulse const register, write-protect         |

| 03H     | PStart  | R/W        | 2           | 0060h          | Active power start threshold setup register, write-protect   |

| 04H     | QStart  | R/W        | 2           | 0120h          | Reactive power start threshold setup register, write-protect |

| 05H     | GPQA    | R/W        | 2           | 0000h          | Channel A power gain register, write-protect                 |

#### Table 2-3 List of RN8209 Registers

Shenzhen RENERGY Micro-Technology Co., Ltd.

| 06H                                        | GPQB    | R/W | 2 | 0000h   | Channel B power gain register, write-protect                                                                                                                            |

|--------------------------------------------|---------|-----|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07H                                        | PhsA    | R/W | 1 | 00h     | Channel A phase calibration register, write-protect                                                                                                                     |

| 08H                                        | PhsB    | R/W | 1 | 00h     | Channel B phase calibration register, write-protect                                                                                                                     |

| 09H                                        | QPhsCal | R/W | 2 | 0000h   | Reactive power phase calibration, write-protect                                                                                                                         |

| 0AH                                        | APOSA   | R/W | 2 | 0000h   | Channel A active power offset register, write-protect                                                                                                                   |

| 0BH                                        | APOSB   | R/W | 2 | 0000h   | Channel B active power offset register, write-protect                                                                                                                   |

| 0CH                                        | RPOSA   | R/W | 2 | 0000h   | Channel A reactive power offset register, write-protect                                                                                                                 |

| 0DH                                        | RPOSB   | R/W | 2 | 0000h   | Channel B reactive power offset register, write-protect                                                                                                                 |

| 0EH                                        | IARMSOS | R/W | 2 | 0000h   | Current Channel A RMS offset calibration, write-protect                                                                                                                 |

| 0FH                                        | IBRMSOS | R/W | 2 | 0000h   | Current Channel B RMS offset calibration, write-protect                                                                                                                 |

| 10H                                        | lBGain  | R/W | 2 | 0000h   | Current Channel B gain setting, write-protect                                                                                                                           |

| 11H                                        | D2FPL   | R/W | 2 | 0000h   | The low 16 bits of custom power register D2FP, write protection                                                                                                         |

| 12H                                        | D2FPH   | R/W | 2 | 0000h   | The high 16 bits of custom power register D2FP, you need to write D2FPH firstly, then write D2FPL, to enable electric energy integration of D2FP only, write-protected. |

| 13H                                        | DCIAH   | R/W | 2 | 0000h   | The high 16 bits of IA channel DC offset correction register, write protection                                                                                          |

| 14H                                        | DCIBH   | R/W | 2 | 0000h   | The high 16 bits of IB channel DC offset correction register, write protection                                                                                          |

| 15H                                        | DCUH    | R/W | 2 | 0000h   | The high 16 bits of U-channel DC offset correction register, write protection                                                                                           |

| 16H                                        | DCL     | R/W | 2 | 0000h   | The low 4 bits of the three DC offset<br>correction registers:<br>DC [11: 0] = {DCU [3: 0], DCIBL [3: 0],<br>DCIAL [3: 0]}, write protection                            |

| 17H                                        | EMUCON2 | R/W | 2 | 0000h   | Metering control register 2, write-protected                                                                                                                            |

| Measurement Parameter and Status Registers |         |     |   |         |                                                                                                                                                                         |

| 20H                                        | PFCnt   | R/W | 2 | 0000h   | Active energy counter register, write-protect                                                                                                                           |

| 21H                                        | DFCnt   | R/W | 2 | 0000h   | Custom energy counter register, write-protect                                                                                                                           |

| 22H                                        | IARMS   | R   | 3 | 000000h | Current A RMS                                                                                                                                                           |

| 23H                                        | IBRMS   | R   | 3 | 000000h | Current B RMS                                                                                                                                                           |

| 24H                                        | URMS    | R   | 3 | 000000h | Voltage RMS                                                                                                                                                             |

| 25H                                        | UFreq   | R   | 2 | 0000h   | Voltage frequency                                                                                                                                                       |

| 26H | PowerPA   | R   | 4     | 0000000<br>0h | Active Power A                                                                                                                                                                                                 |

|-----|-----------|-----|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27H | PowerPB   | R   | 4     | 0000000<br>0h | Active Power B                                                                                                                                                                                                 |

| 28H | PowerQ    | R   | 4     | 0000000<br>0h | Reactive power                                                                                                                                                                                                 |

| 29H | EnergyP   | R   | 3     | 000000h       | Active energy, configurable for being cleared<br>or not after read by EnergyCLR register, with<br>defaulf of being not cleared after read.                                                                     |

| 2AH | EnergyP2  | R   | 3     | 000000h       | Active energy, configurable for register being cleared after read or freezing register, with defaulf of being cleared after read.                                                                              |

| 2BH | EnergyD   | R   | 3     | 000000h       | Reactive energy or user-defined energy, configurable for register being cleared or not after read, with register being not cleared after read as default which is controlled by the bit of EnergyCLR register. |

| 2CH | EnergyD2  | R   | 3     | 000000h       | Reactive energy or user-defined energy,<br>configurable for register being cleared after<br>read or freezing register, with register being<br>cleared after read as default                                    |

| 2DH | EMUStatus | R   | 3     | 00EE79h       | Energy measurement status and checksum register                                                                                                                                                                |

| 30H | SPL_IA    | R   | 3     | 000000h       | Sample value of IA channel ADC                                                                                                                                                                                 |

| 31H | SPL_IB    | R   | 3     | 000000h       | Sample value of IB channel ADC                                                                                                                                                                                 |

| 32H | SPL_U     | R   | 3     | 000000h       | Sample value of U channel ADC                                                                                                                                                                                  |

| 35H | UFreq2    | R   | 3     | 000000h       | Voltage frequency register 2 with extended range of frequency measurement, it will output the same value with UFreq(0x25H) when the frequency is 50Hz on voltage channel.                                      |

|     |           |     | Int   | errupt Regis  | sters                                                                                                                                                                                                          |

| 40H | IE        | R/W | 1     | 00h           | Interrupt enable register, write-protect                                                                                                                                                                       |

| 41H | IF        | R   | 1     | 00h           | Interrupt flag register, cleared after read                                                                                                                                                                    |

| 42H | RIF       | R   | 1     | 00h           | Reset interrupt flag register, cleared after read                                                                                                                                                              |

|     |           |     | Syste | m Status Re   | gisters                                                                                                                                                                                                        |

| 43H | SysStatus | R   | 1     |               | System status register                                                                                                                                                                                         |

| 44H | RData     | R   | 4     |               | Previous SPI/UART data read out                                                                                                                                                                                |

| 45H | WData     | R   | 2     |               | Previous SPI/UART data written                                                                                                                                                                                 |

| 7FH | DeviceID  | R   | 3     | 820900h       | RN8209 Device ID                                                                                                                                                                                               |

|     | -         |     |       |               |                                                                                                                                                                                                                |

# 2.12.2 Calibration parameter registers

#### System control registers

SYSTEM Control Register (SYSCON) Address: 0x00 H Default Value: 0003H

| Bit      | Bit Name    | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 15       | Reserved    | The default value is 0, do not write 1 to this bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 14-<br>8 | Uartbr[6:0] | UART baud rate selection, read-only, and its value is determined by the hardware<br>pin B1 and B0<br>{B1, B0} = 00, Uadrbr = 7'h2E, 2400 baud<br>{B1, B0} = 01, Uadrbr = 7'h16, 4800 baud<br>{B1, B0} = 10, Uadrbr = 7'h0B, 9600 baud<br>{B1, B0} = 11, Uadrbr = 7'h05, 19200 baud<br>It only makes sense when the UART is selected as the communication interface,<br>and when SPI is selected, it will be 0.<br>Note: The uartbr[6:0] will be added in the checksum calculation, so that it will influce<br>the result of the checksum when the UART is chosen as the communication<br>interface. The baudrate of RN8209C is fixed at 4800. |  |  |  |  |

| 7        | Reserved    | The default value is 0, do not write 1 to this bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 6        | ADC2ON      | ADC2ON = 1: indicates that ADC Current Channel B is on; = 0: ADC Current Channel B closed, ADC output is fixed to 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 5-4      | PGAIB[1:0]  | Analog gain selection of current Channel BPGAIB1PGAIB0current<br>channel B00PGA=101PGA=210PGA=41PGA=4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 3-2      | PGAU[1:0]   | Voltage channel analog gain selectionPGAU1PGAU0voltage<br>channel00PGA=101PGA=210PGA=411PGA=4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 1-0      | PGAIA[1:0]  | Current Channel A analog gain selection, 16 times by default.PGAIA1PGAIA0current<br>channel A00PGA=101PGA=210PGA=811PGA=16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

# **Measurement Control Registers**

Measurement control registers are used for settings of energy measurement functions.

| Energy Measure Control Register (EMUCON) Address: 0x01 H Default Value: 0003H |           |                                                                                                                             |  |  |  |

|-------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit Bit Name Descriptions                                                     |           |                                                                                                                             |  |  |  |

| 15                                                                            | EnergyCLR | The default value is 0<br>= 0: 29 / 2B-accumulated energy registers;<br>= 1: 29 / 2B energy register is cleared after read; |  |  |  |

|       |           | HPFIRC            | )FF = ∩· I                                                                                                                | Enable the digital high-pass filter of IB channel                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|-------|-----------|-------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 14    | HPFIBOFF  |                   |                                                                                                                           | Disable the digital high-pass filter of IB channel                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|       |           | Custom            | om energy accumulation mode selection:<br>D QMOD0 Accumulative power Qm                                                   |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           | QMOD<br>1         | QMOD0                                                                                                                     | Accumulative power Qm                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 13-12 | QMOD[1:0] | 0                 | 0                                                                                                                         | If Qm = DataQ, the positive and negative power will be<br>involved in accumulation, and the negative power will have<br>an REVQ symbol.                                                                                                                              |  |  |  |  |  |  |  |  |

|       |           | 0                 | 1                                                                                                                         | Only positive power is accumulated.                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

|       |           | 1                 | 0                                                                                                                         | If Qm= DataQ , the positive and negative power will be<br>involved in accumulation, and the negative power will have<br>no REVQ symbol.                                                                                                                              |  |  |  |  |  |  |  |  |

|       |           | 1                 | 1                                                                                                                         | Qm = DataQ (reserved)                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| 11-10 | PMOD[1:0] |                   | tive energy accumulation mode selection: same as the reactive energy cumulation in the table above.                       |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   | e ZX output initial value is 0, and different waveforms will be output according                                          |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   |                                                                                                                           | D0 configuration:<br>, it means that only at the selected zero-crossing, the ZX output                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| 9     | ZXD1      | change            | nges;                                                                                                                     |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   | nen ZXD1 = 1, it means that at the positive and negative zero-crossing points, e ZX outputs changes.                      |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   |                                                                                                                           | , it means that the positive zero-crossing point is selected as a                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 8     | ZXD0      |                   | •                                                                                                                         | tection signal;<br>, it means that the negative zero-crossing point is selected as a                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

|       |           |                   |                                                                                                                           | tection signal;                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 7     | ZXCFG     |                   |                                                                                                                           | pin IRQ_N / ZX / SIG serves as IRQ_N.<br>pin IRQ_N / ZX / SIG serves as ZX.                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 6     | HPFIOFF   | HPF IOF           | F = 0: Er                                                                                                                 | nable IA channel digital high-pass filters                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| 0     |           |                   |                                                                                                                           | isable IA channel digital high-pass filters                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| 5     | HPFUOFF   |                   |                                                                                                                           | Enable U-channel digital high-pass filters<br>Disable U-channel digital high-pass filters                                                                                                                                                                            |  |  |  |  |  |  |  |  |

| 4     | CFSUEN    | CFSUE<br>output r | N = 1, tl<br>ate will b                                                                                                   | control bit of the PF / QF pulse output acceleration module. When<br>he pulse acceleration module will be enabled, and the pulse<br>be increased by $2^{(CFSU [1:0] +1)}$ times. When CFSUEN = 0,<br>eration module will be disabled, and the pulse will have normal |  |  |  |  |  |  |  |  |

| 3,2   | CFSU[1:0] | This bit          | This bit will work with the help of CFSUEN. See CFSUEN instructions.                                                      |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   | en QRUN = 1, enable the QF pulse output and custom energy register                                                        |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 1     | DRUN      | When (            | cumulation;<br>nen QRUN = 0, disable the QF pulse output and custom energy register<br>cumulation, with the default of 1. |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

|       |           |                   | en PRUN = 1, enable the PF pulse output and active energy register                                                        |                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| 0     | PRUN      |                   | PRUN =                                                                                                                    | 0, disable the PF pulse output and active energy register the the default of 1.                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

#### Pulse frequency registers

| High Freq | uency Impulse C | onst Register | (HFConst) | Addre  | ess: 0x 02 | H Default \ | Value : 10 | 00H  |

|-----------|-----------------|---------------|-----------|--------|------------|-------------|------------|------|

|           | Bit15           | 14            | 13        | 12     | 11         | 10          | 9          | Bit8 |

| Read:     | HFC15           | HFC14         | HFC13     | HFC12  | HFC11      | HFC10       | HFC9       | HFC8 |

| Write:    | HFC13           |               |           |        |            |             | пгсэ       |      |

| Reset:    | 0               | 0             | 0         | 1      | 0          | 0           | 0          | 0    |

| :         | Bit7            | 6             | 5         | 4      | 3          | 2           | 1          | Bit0 |

| Read      | HFC7            | HFC6          | HFC5      | HFC4   | HFC3       | HFC2        | HFC1       | HFC0 |

| Write:    |                 |               | 11 05     | 111 04 | 11 03      | 111 02      |            |      |

| Reset:    | 0               | 0             | 0         | 0      | 0          | 0           | 0          | 0    |

HFConst is a 16-bit unsigned number, it should be compared with 2 times of the absolute value of the fast pulse counter register PFCNT / DFCNT register value. If the result is greater than or equal to the HFConst, then there will be corresponding PF / QF pulse output.

#### No-load and start threshold registers

| Start  |       | shold Setup F<br>Start) | Register | Address: 0x 03h Default Value : 0060H |      |      |       |      |  |

|--------|-------|-------------------------|----------|---------------------------------------|------|------|-------|------|--|

|        | Bit15 | 14                      | 13       | 12                                    | 11   | 10   | 9     | Bit8 |  |

| Read:  | PS15  | PS 14                   | PS 13    | PS 12                                 | PS11 | PS10 | PS 9  | PS 8 |  |

| Write: | FOIJ  | FO 14                   | F0 10    | F3 12                                 | FOIT | F310 | F 3 9 | FSO  |  |

| Reset: | 0     | 0                       | 0        | 0                                     | 0    | 0    | 0     | 0    |  |

|        | Bit7  | 6                       | 5        | 4                                     | 3    | 2    | 1     | Bit0 |  |

| Read:  | PS7   | PS 6                    | PS 5     | PS 4                                  | PS 3 | PS 2 | PS 1  | PS 0 |  |

| Write: |       |                         |          |                                       |      |      |       |      |  |

| Reset: | 0     | 1                       | 1        | 0                                     | 0    | 0    | 0     | 0    |  |

| Start P<br>(DStart) |       | hold Setup | Register | Address: | 0x 04h Defa | ult Value : 0 | 120H         |      |

|---------------------|-------|------------|----------|----------|-------------|---------------|--------------|------|

|                     | Bit15 | 14         | 13       | 12       | 11          | 10            | 9            | Bit8 |

| Read:               | QS15  | QS 14      | QS 13    | QS 12    | QS11        | QS10          | QS 9         | QS 8 |

| Write:              | 0315  | QO 14      | QS 13    | Q3 12    | QOT         | 0010          | Q3 9         | Q3 0 |

| Reset:              | 0     | 0          | 0        | 0        | 0           | 0             | 0            | 1    |

|                     | Bit7  | 6          | 5        | 4        | 3           | 2             | 1            | Bit0 |

| Read:               | QS7   | QS 6       | QS 5     | QS 4     | QS 3        | QS 2          | QS 1         | QS 0 |

| Write:              | 491   | 430        | 435      | Q3 4     | 433         | Q3 Z          | <b>U</b> 3 I | Q3 U |

| Reset:              | 0     | 0          | 1        | 0        | 0           | 0             | 0            | 0    |

The start threshold can be configured by PStart and QStart registers. They are 16-bit unsigned numbers, and when compared, they should be compared with the high 24-bit absolute value of PowerP and DataD (a 32-bit signed number) to judge the start status.

When |PowerP| is smaller than PStart, PF does not output any pulse.

When |DataD| is smaller than DStart, QF does not output any pulse.

## Gain calibration register

| Power ( | Gain Registe | r A(GPQA) | Address: 0 | 05h Default Value : 0 | 000H   |        |        |

|---------|--------------|-----------|------------|-----------------------|--------|--------|--------|

|         | Bit15        | 14        | 13         | 12 3                  | 2      | 1      | Bit0   |

| Read:   | GPQA 15      |           |            | GPQA 12GPQA 3         |        | GPQA 1 | GPQA 0 |

| Write:  | GFQA_15      | GFQA_14   | GFQA_13    | GFQA_12GFQA_3         | GFQA_2 | GFQA_1 | GFQA_0 |

| Reset:  | 0            | 0         | 0          | 0                     | 0      | 0      | 0      |

| Power ( | Gain Registe | r B(GPQB) | Address: 0 | x06h Default Value : 0 | 000H   |   |        |

|---------|--------------|-----------|------------|------------------------|--------|---|--------|

|         | Bit15        | 14        | 13         | 12 3                   | 2      | 1 | Bit0   |

| Read:   |              |           | CDOP 12    |                        |        |   |        |

| Write:  |              |           | GPQD_13    | GPQB_12GPQB_3          | GPQD_2 |   | GPQB_0 |

| Reset:  | 0            | 0         | 0          | 0                      | 0      | 0 | 0      |